Nuevas informaciones apuntan a que el retraso de la litografía de los 10nm de Intel tendría los días contados ante de salir ya que la litografía de los 7nm está muy madura.

Intel inicialmente tenía planeada la litografía de los 10nm para 2016, pero la compañía se ha encontrado con más problemas de los esperados y están trabajando a contrarreloj para que esta llegue al mercado lo antes posible al mercado en forma de procesadores. El proceso actualmente solo permite crear algo más del 50% de los procesadores viables y esto impide comercializarlos, ya que llegarían a un precio absurdamente elevado, esperándose la producción en masa para finales de 2019. Esto ha supuesto un problema para la compañía, tanto en línea de productos como de negocio.

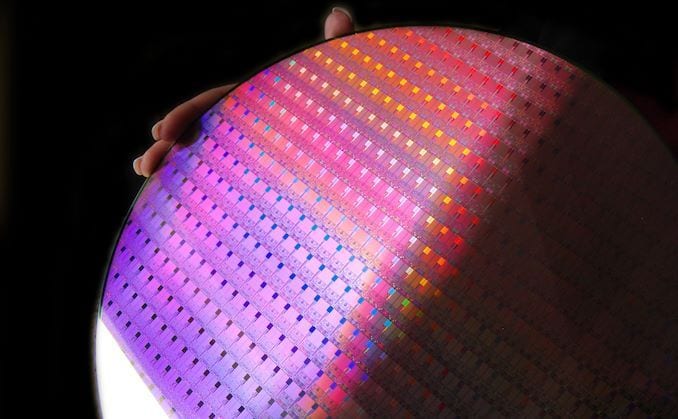

La litografía de los 10nm de Intel está siendo un dolor de cabeza importante para la compañía.

Según informaciones de Anandtech la litografía de los 10nm podría tener una vida bastante corta, ya que la compañía ha seguido desarrollando los 7nm la cual estaría evolucionando conforme a lo esperado y entraría dentro del Roadmap original de la compañía.

En varias ocasiones la compañía ha dicho que la densidad de escala de los transistores es demasiado agresiva para el proceso de fabricación de los 10nm, siendo el principal problema que ha tenido la compañía con esta litografía.

La nueva litografía de Intel de los 10nm se basa enteramente en la litografía ultravioleta profunda (DUVL) con láseres que fusionan a una longitud de onda de 193mm. Para habilitar estos tamaños de características finas Intel se propuso conseguir los 10nm, mediante un proceso de uso intensivo de múltiples patrones. El problema de este proceso según la compañía es que es el uso intensivo de los múltiples patrones concretamente.

Producir en base a los 7nm de Intel es usar la litografía ultravioleta extrema (EUVL) con una longitud de onda laser de 13.5nm para capas seleccionadas, reduciendo el uso de los múltiples patrones para ciertas capas metálicas y por tanto, se simplifica el tiempo de producción y se acortan los ciclos.

Aparentemente los 7nm se han desarrollado de manera paralela a los 10nm y por un equipo de desarrollo completamente diferentes. El resultado de este desarrollo está en marca y se proyecta en el HVM de acuerdo con el Roadmap de la compañía. Se comenta que Murthy Renduchintala, Director de Ingeniería y Presidente de Tecnología, Arquitectura de Sistemas y Grupos de Clientes de la compañía dijo lo siguiente durante la 39ª Conferencia de Inversores del Nasdaq:

“7nm para nosotros es un equipo separado y en gran parte un esfuerzo separado”

“Estamos muy satisfechos con nuestro progreso de 7nm. De hecho, muy contento co nuestro progreso en 7nm. Creo que hemos tomado muchas lecciones de la experiencia de 10nm, ya que definimos eso y definimos un punto de optimización diferente entre la densidad, la potencia y el rendimiento del transistor y la previsibilidad del cronograma […] Por lo tanto, estamos muy, muy enfocados en obtener 7nm según nuestros planes internos originales”

“Una cosa que voy a decir es que, si nos fijamos en 7nm, para nosotros este es realmente un momento en el tiempo en el que dispondremos de nuevo el EUV en la matriz de fabricación y, por lo tanto, creo que eso nos dará un cierto grado de retorno a la cadencia tradicional de la Ley de Moore”

“[Con los 7nm] Estamos volviendo más a un factor de escalado de 2X […] y luego seguimos avanzando con ese objetivo”.