PCIe 6.0: Publicados los datos de la versión 0.3 del nuevo estándar por parte de PCI-SIG

Se ha anunciado por parte del consorcio PCI-SIG la versión 0.3 del estándar PCIe 6.0, la cual debería estar ultimada para el año 2021.

Actualmente los procesadores de Intel ofrecen soporte para el estándar PCIe 3.0, mientras que AMD ofrece ya el PCIe 4.0. Tanto Intel como AMD trabajan en CCX, un estándar de comunicación bajo PCIe 5.0. Pero estos ya han quedado ‘obsoletos’ gracias a la Peripheral Component Interconnect Special Interest Group (PCI-SIG). Este consorcio ha anunciado las especificaciones de la interfaz PCIe 6.0 en su versión 0.3.

Este protocolo de comunicación aún está en una fase primaria de desarrollo y falta bastante para que esté completa. Se empezó a desarrollar el PCIe 6.0 hace unos meses y en 2021 debería estar plenamente desarrollado. Su implementación debería poder empezar en 2022-2023, aunque lo más probable es que hasta 2023 no se empezaría a utilizar.

PCI-SIG anuncia la versión 0.3 del estándar PCIe 6.0

Las especificaciones finales deberían estar listas en 2021 y su implementación en placas base ya seria para 2023, muy probablemente. El estándar PCIe 4.0 se anunció en 2017 y se ha empezado a implementar por parte de AMD este año. PCIe 5.0 se anunció hace unos meses y no se empezará a implementar hasta 2021.

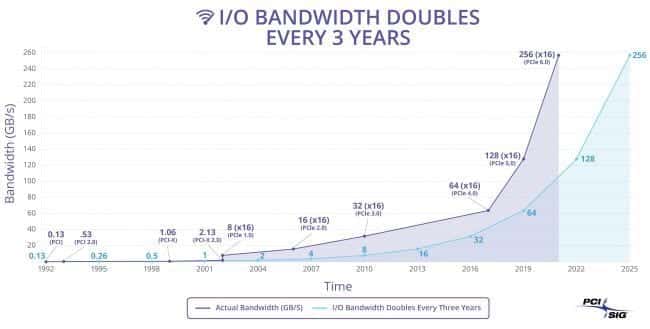

La interfaz PCIe 6.0 nos ofrece una velocidad de transmisión de datos de hasta 64GT/s, que es el doble con respecto al PCIe 5.0. Esta interfaz nos ofrecerá 7 880MB/s por cada pista. Así el puerto PCIe 3.0 x16 nos ofrecerá una velocidad de datos próxima a los 128Gb/s. La PCI-SIG busca siempre duplicar las especificaciones de velocidad con respecto a la generación anterior.

Como suele ser habitual, el PCIe 6.0 soportar los estándares anteriores, algo en lo que suele insistir el consorcio.

Esta interfaz tendrá dos cambios importantes, siendo uno la codificación PAM-4 (Pulse Amplitude Modulation with four levels). Dicha tecnología usa los estándares de redes de ultra alta gama. Se ha implementado la corrección de errores de avance (Forward Error Correction / FEC) de baja latencia. Esta tecnología nos ofrece mecanismos de alta eficiencia para el ancho de banda.

Fuente: TH